Propeller Manual V1.01 Japanese

この文書に関する注意事項

この文書は、わたくし新渡戸広明が自分の学習の為に、かなりてきとーにちゃちゃっとかつだらだらと作成途上のものです。そして何よりも、この Wiki 自体の TextFormattingRules の学習という側面が強いという事実を否めません。なんちゃって翻訳という性格上、この文書の翻訳の正当性、妥当性、信頼性は保障いたしかねます(というか、全くありません)ので悪しからず。

厳密かつ完全なものをお望みでしたら、ご自身で原文Propeller Manual v1.01を紐解いていただくのが最善の方策と存じます。画像もとても粗いのでオリジナルをご覧になることを強くお勧め致します。

もし、この翻訳作業に協力していただける奇特な方がいらっしゃいましたら、nitobe@saigyo.net までご連絡ください。当 Wiki の編集作業に参加していただく事は吝かではございません。検討のうえ、ID / Password を発行させていただきます。

第一章:プロペラ・チップの紹介

この章では、プロペラ・チップのハードウエアを記述します。最初にプロペラのハードウエア構造を理解することは、プロペラを効果的かつ完全に理解して使うために有意義なことです。ここでは、パッケージの種類、パッケージの大きさ、ピンの説明と機能などのハードウエアの詳細を示します。

概念

プロペラ・チップは、組み込みシステム用途で、低消費電流と小型化を保持しつつ、高速処理ができる様に設計されています。高速であるのみならず、プロペラは学習と利用が簡単な比較的単純な構造で、同時かつ独立に協調作業ができる、コグと呼ばれる8台の処理装置により、その柔軟性と威力を発揮します。結果的に、プロペラによる設計は、アプリケーション開発者を組み込みシステム・プログラミングの一般的な煩雑さから開放します。例えば:

- 平坦なメモリ空間。コード、データまたは変数領域において、ページングを考慮する必要がありません。このことは、アプリケーション開発における大きな時間節約となり得ます。

- 非同期イベントは割り込みを使用した装置よりも取り扱うのが簡単です。プロペラは割り込みの必要がありません。若干のコグを個々の広帯域のタスクに割り当てて、他のコグから干渉しないようにしておいてください。結果的に、保守しやすい、より敏感なアプリケーションにすることができます。

- プロペラ・アッセンブリ言語は、条件実行と結果付加書式を特徴とする基本命令の集まりです。特に重要なのは、コードの複数の決定領域が一貫して時間を計測されることです。イベント・ハンドラは神経質になる必要はありません、そして、開発者は随所でのタイミング合わせの為の命令の追加や圧縮による時間を浪費しません。

パッケージの種類

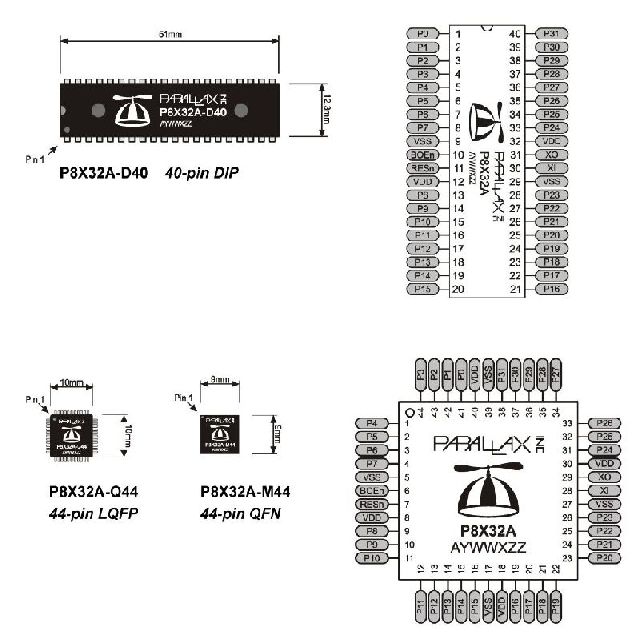

プロペラ・チップはここで示されるパッケージが利用できます。

- 図1-0:

ピン説明

| 表1-1:ピン説明 | ||

|---|---|---|

| ピン名 | 方向 | 説明 |

| P0-P31 | I/O | 汎用I/OポートA。 |

| 1ポート30mAソース/シンク(3.3VDC)グループ全体で100mAソース/シンクを上回らないこと。論理閾地 ≒ 1/2 VDD ; 1.65VDC @ 3.3VDC | ||

| 下で示されるピンには、パワーアップ/リセットと同時に特別な目的があるが、その他は汎用 I/O です。 | ||

| P28 - オプションの、外部EEPROMへのI2C SCL接続。 | ||

| P29 - オプションの、外部EEPROMへのI2C SDA接続。 | ||

| P30 - ホストへのシリアル通信 Tx。 | ||

| P31 - ホストからのシリアル通信 Rx。 | ||

| VDD | − | 電源 3.3V (2.7-3.3VDC) |

| VSS | − | グランド |

| BOEn | I | ブラウン・アウト・イネーブル(アクティブ・ロー) |

| VDD もしくは VSS に接続してください。 | ||

| VSS 接続の場合: | ||

| RESn は監視可能な弱出力(5KΩを経由した VDD )となり、かつロー・レベル入力によりリセットも可能です。 | ||

| VDD 接続の場合: | ||

| RESn はシュミット・トリガの CMOS 入力となります。 | ||

| RESn | I/O | リセット(アクティブ・ロー) |

| ロー・レベルの場合:プロペラ・チップはリセットされます。全てのコグは使用不能、全ての I/O ピンはフローティング状態となります。RESn が、ロー・レベルからハイ・レベルに遷移してから50mS 後に動作を再開します。 | ||

| XI | I | 水晶発振子入力 |

| XO を未接続とし、水晶発信器の出力と接続します。もしくは CLK レジスタの設定により、水晶発振子または、共鳴器を XO と共に接続します。外部抵抗またはコンデンサは不要です。 | ||

| XO | O | 水晶発振子出力 |

| 外部の水晶発振子のためのフィードバックを提供します。CLK レジスタの設定により、未接続となります。外部抵抗またはコンデンサは不要です。 | ||

プロペラP8X32Aは 32 本の I/O ピン(ポートA、P0 から P31)を持っています。 これらのI/Oピンの4つ、P28-P31 には、パワーアップ/リセットと同時に特別な目的があります。 パワーアップ/リセット時、P30 と P31 はプログラミングの為、ホストと通信します。 そして、P28 と P29 は、外部の 32kByte EEPROM (24LC256) と接続します。

仕様

| 表1-2:仕様 | |

|---|---|

| モデル | P8X32A |

| 要求電源 | 3.3 ボルト 直流 |

| 外部クロック速度 | DC 〜 80MHz (4MHz - 8MHz クロック PLL 使用) |

| システム・クロック速度 | DC 〜 80MHz |

| 内部 RC 発信器 | 12MHz または 20kHz (概算;それぞれ 8MHz-20MHz または 13kHz-33kHzの変動) |

| 主記憶装置 RAM/ROM | 64kBytes; 32kB RAM + 32kB ROM |

| コグ RAM | 512 x 32 bits /コグ |

| RAM/ROM 構成 | ロング(32-bit)、ワード(16-BIT)およびバイト(8-BIT) アドレス指定可能 |

| I/O ピン | VDD/2 閾値 CMOS x 32 ピン |

| ソース/シンク電流 | 30mA/ピン |

| ソース/シンク電流 | 100mA/8ピン |

| 消費電流 @3.3VDC 70°F | 500uA/MIPS (MIPS = Freq in MHz / 4 * 有効コグ) |

ハードウエア接続

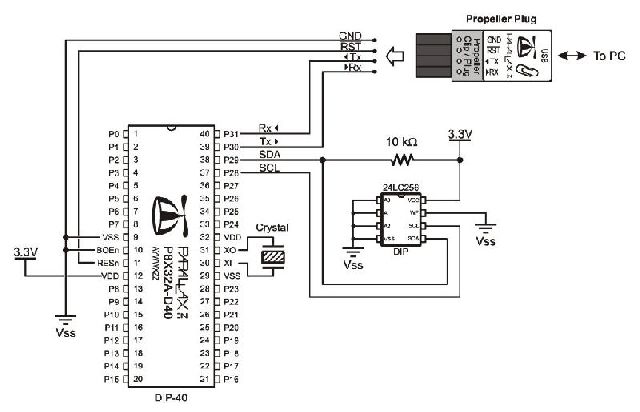

図1-1は、ホストとEEPROMアクセスをプロペラ・チップに提供する配線図の一例を表します。この例では、ホスト・アクセスは、プロペラ・チップ(USB-TTL シリアル通信変換機)によって成し遂げられます。

- 図1-1:プロペラ・チップと外部32Kbyte EEPROMをプログラムして、外部の水晶発振子でプロペラを走らせることを想定した配線図の例

起動時手順

パワーアップ(+ 100ms)、RESnのロー・ハイ遷移またはソフトウェア・リセットと同時に:

- プロペラ・チップは遅いモード(20KHz)でその内部クロックを始動して、50ms(リセット待ち)後、内部クロックを速いモード(12MHz)に切り替え、内臓のブート・ローダ・プログラムを、最初の処理装置(コグ0)に展開し実行します。

- ブート・ローダは以下のタスクを順に実行します。

- a. ピンP30とP31でホスト(例えばPC)からの通信を検査します。ホストからの通信が検出できたら、ブート・ローダはプロペラ・チップを確認して、メイン・RAM か、外部32KBのEEPROMにプログラムをダウンロードするためにホストと通信します。

- b. ホストからの通信が検出できなかったら、ブート・ローダはピンP28とP29で外部32KBのEEPROM(24LC256)を検査します。EEPROMが検出できたら、32KBの全てのデータ・イメージはプロペラ・チップのメイン・RAM に転送されます。

- c. EEPROMが検出できなかったら、ブート・ローダは停止、Cog 0は終了されます、プロペラ・チップのすべてのI/Oピンは入力に固定され、シャットダウンモードに移行します。

- ステップ2aか2bによりプログラムのメイン・RAM への転送に成功し、かつ停止命令がホストによって与えられなければ、コグ0は内臓 Spin インタプリタを再展開され、ユーザ・コードはメイン・RAMから実行されます。

実行時手順

プロペラ・アプリケーションは、バイナリ型式にコンパイルされ、プロペラ・チップの RAM もしくは外部 EEPROM にダウンロードされるユーザ・プログラムです。アプリケーションは、プロペラ・チップの Spin 言語(高級言語)と、オプションのプロペラ・アッセンブリ言語構成要素(低級言語)で記述されるコードから成ります。Spin言語で書かれたコードは Spin インタプリタを走らせているコグで実行時に解釈され、プロペラ・アッセンブリで書かれたコードは純粋な形で直接コグで実行されます。あらゆるプロペラ・アプリケーションは少なくとも少しの Spin コードから成って、実際には、Spin で、または、多彩な Spin とアッセンブリで完全に書かれるかもしれません。プロペラ・チップの Spin インタプリタは、アプリケーションを動作するようにするために、前述の起動手順のステップ3で始まります。

一度、起動手順が終了し、コグ0でアプリケーションが実行されたら、すべての次の動作はアプリケーションそのものによって定義されます。アプリケーションは内部のクロック・スピード、I/Oピン使用、構成レジスタのようなものの完全な制御が可能です、いつでも、何でも、どうやってでも、多くのコグはどんな所定の時刻にでも走っています。内部のクロックスピードを含む全ては実行時にアプリケーションで制御できるばかりでなく変更も可能です。第3章:プロペラ・プログラミング・チュートリアルを参照してください。

停止時手順

プロペラが停止状態になるとき、すべてのコグを停止する為に内部クロックが停止します、そして、すべてのI/Oピンは入力方向(高インピーダンス)に設定されます。停止状態は、以下の3つの事象のうちのひとつによって引き起こされます:

- 電圧低下回路が使用可能かつ VDD が電圧低下閾値(2.7VDC)以下に落ちている、

- RESn ピンがロー・レベルになっている、あるいは、

- アプリケーションが再起動を要求している。(292 ページ REBOOT 命令参照)

VDD 電圧レベルが電圧低下閾値から復帰し、かつRESnピンがハイ・レベルのとき、停止状態は中断します。

ブロック図

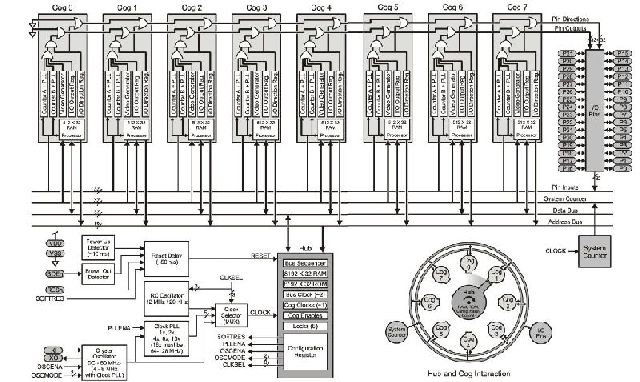

コグとハブの相互作用は、プロペラ・チップにとって極めて重大です。ハブはどのコグが排他的な資源にアクセスすることができるかについて制御します、タイミングを決定的にしておくために、いくつのコグが走っているかどうかにかかわらず主記憶装置 RAM/ROM、構成レジスター、その他について、ハブは「総当り戦」方式で一つずつあらゆるコグに排他的なアクセス権を与えます。

- 図1-2:プロペラ・チップ・ブロック図

共有資源

プロペラには2種類の共有資源があります:

- 共有資源

- 相互排他資源

共有資源は、多くのコグでいつでもアクセスできます。相互排他資源は、多くのコグのうち、一度にひとつのコグだけがアクセスできます。共有資源は、I/O ピンとシステム・カウンタです。他の全ての共有資源は、本来、排他的です、そして、そのアクセスは、ハブで制御されます。24 ページのハブの章を参照してください。

システム・クロック

システム・クロック(図1-2の中の「CLOCK」として示される)は、プロペラ・チップのほとんどすべての構成要素のための中心クロック源です。システム・クロック信号は、3つの可能な供給源のうちの1つから供給されます:

- ) 内臓 RC 発信器、

- ) クロック・フェーズロックド・ループ (PLL) または、

- ) 水晶発振器(外部の水晶発振子または水晶/発信器パックで供給される内臓回路)

供給源は CLK レジスタの設定に従って測定されます。そしてそれは、コンパイル時または実行時で選択可能です。直接システム・クロックを使わない唯一の構成要素は、ハブとバスです;それらは、2つの(2)によってシステム・クロックを分周します。

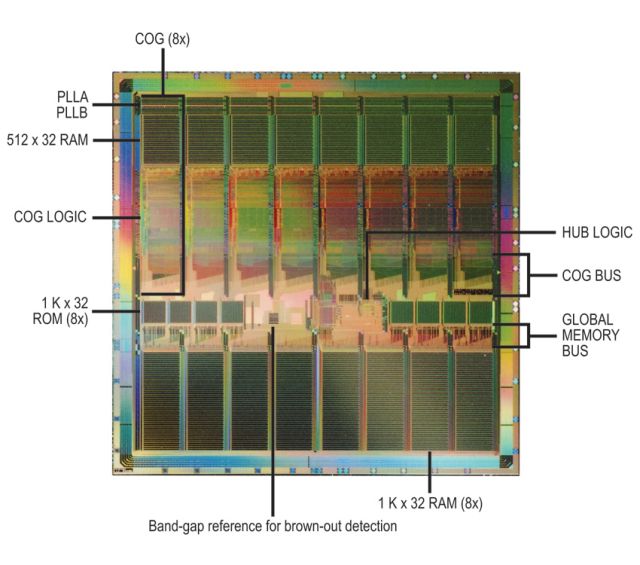

コグ(処理装置)

プロペラはコグと呼ばれる0番から7番の8台の処理装置を含んでいます。それぞれのコグは同様の構成要素を含みます(図1-2参照)。それは、処理ブロック、512ロング構成(512 x 32 ビット)の 2kByte ローカル RAM。そして、2つの PLL 付 I/O 補助レジスタ、ビデオ信号発生器、I/O 出力レジスタ、I/O 方向レジスタです。但しこの図にはその他のレジスタが省略されています。コグ・レジスターの完全なリストについては、表1-3を参照てください。それぞれのコグは同様だが他のコグとは独立して動作出来るように厳密に設計されています。

すべての8つのコグは同じクロック源(システム・クロック)で動くので、これら各々は同じ時間参照を維持します、そして、すべてのアクティブなコグは同時に指示を実行します。前述のシステム・クロックを参照してください。これらは、すべて同じ共有資源(I/Oピン、主記憶装置 RAMとシステム・カウンタのような)にアクセスします。前述の共有資源を参照してください。 独立して、または、主記憶 RAM による他のコグからの調整でどちらでも、コグは実行時に起動や停止が出来、また、同時に仕事を果たすようにプログラムできます。それらの使用の性質に関係なく、プロペラ・アプリケーション・デザイナーはそれぞれのコグが使用される方法と時間に対する完全な支配をします;コンパイラに起因するにせよ、オペレーティングシステムに起因するにせよ、複数の歯車の間には仕事の分裂がありません。この方法は、絶対的決定論的なタイミング、消費電力と反応を組込形アプリケーションで達成する権限を開発者に与えます。

それぞれのコグはそれ自身の RAM を備えています。そして、コグ RAM と呼ばれています。そして、それはそれぞれ32ビットの512のレジスタで構成されています。表1-3で記述されるように、コグ RAM は最後の16のレジスター(それは専用レジスタです)以外はすべて汎用 RAM です。コグ RAMは実行コード、データ、変数のために使われます、そして、最後の16の場所はシステム・カウンタ、I/Oピンとローカル・コグ周辺機器へのインターフェースとして用いられます。

コグが立ち上げられるとき、0($000)番地から495($1EF)番地は主記憶装置 RAM/ROMとその特別な目的場所から順番に転送されます、496($1F0)番地から511($1FF)番地はゼロで消去されます。転送後、コグはコグ RAM の0($000)番地から命令の実行を開始します。それ自身か他のコグによって停止もしくは再起動させられるか、リセットが発生するまでコードを実行し続けます。

| 表1-3: コグ RAM 専用レジスタ | |||

|---|---|---|---|

| 番地 | 名称 | 類型 | 記述 |

| $1F0 | PAR | 読込のみ*1 | ブート・パラメータ |

| $1F1 | CNT | 読込のみ*1 | システム・カウンタ |

| $1F2 | INA | 読込のみ*1 | 入力状況 P31 - P0 |

| $1F3 | INB | 読込のみ*1 | 入力状況 P63 - P32*2 |

| $1F4 | OUTA | 読/書 | 出力状況 P31 - P0 |

| $1F5 | OUTB | 読/書 | 出力状況 P63 - P32*2 |

| $1F6 | DIRA | 読/書 | 方向状況 P31 - P0 |

| $1F7 | DIRB | 読/書 | 方向状況 P63 - P32*2 |

| $1F8 | CTRA | 読/書 | カウンタ A 制御 |

| $1F9 | CTRB | 読/書 | カウンタ B 制御 |

| $1FA | FRQA | 読/書 | カウンタ A 周波数 |

| $1FB | FRQB | 読/書 | カウンタ B 周波数 |

| $1FC | PHSA | 読/書 | カウンタ A 位相 |

| $1FD | PHSB | 読/書 | カウンタ B 位相 |

| $1FE | VCFG | 読/書 | ビデオ設定 |

| $1FF | VSCL | 読/書 | ビデオ倍率 |

注1: ソース・レジスタとして参照のみ(例: MOV DEST, SOURCE).

注2: 将来の為に予約済み

それぞれの専用レジスタは以下の方法でアクセス出来ます:

- ) その物理レジスタ番地、

- ) そのあらかじめ定義された名前、あるいは、

- ) 0-15の偏位によるレジスタ配列変数。

以下は、プロペラ・アッセンブリによる例です。

MOV $1F4, #$FF 'Set OUTA 7:0 high MOV OUTA, #$FF 'Same as above

以下は、Spin 言語による例です。

SPR[$4] := $FF 'Set OUTA 7:0 high OUTA := $FF 'Same as above

ハブ

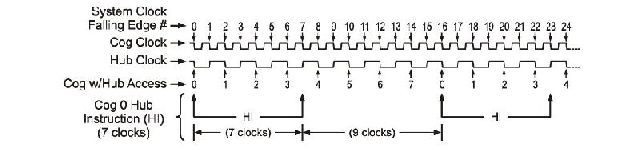

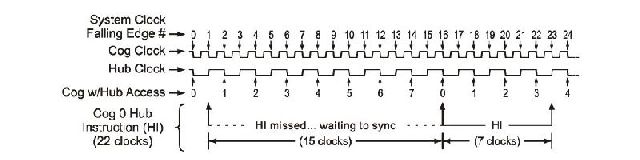

システムの完全性を維持するために、互いに排他的な資源は、一度に複数のコグでアクセスされてはいけません。ハブは排他的な資源へのアクセスをコントロールすることによってこの完全性を維持します。コグ0からコグ7へそしてコグ0に戻る「総当たり戦」方式でそれぞれのコグに順次アクセス権を与えます。ハブと、それが制御するバスは、システム・クロックの半分の速度で走ります。これは、ハブがコグに排他的資源へのアクセスを16システム・クロック周期で一度与えることを意味します。ハブ操作(排他的資源にアクセスするプロペラ・アッセンブリ)は7サイクルの実行を必要とします、ただし、それは最初にハブ・アクセス・ウインドウの始まりに同期する必要があります。ハブ操作を実行するためにハブ・アクセス・ウインドウは、さらに7サイクルまで同期するために最高15のサイクル(我々がちょうどそれを逃すならば、16引く1)かかるので、ハブ操作は7から22サイクルまでを必要とします。

図1-3と図1-4は、コグ0が実行するハブ操作をする例を表します。図1-3は、最高の状態のシナリオを表します;ハブ操作は、運よく正にそのコグのアクセス・ウインドウの始まりでした。ハブ操作の命令実行を即座に行い(7サイクル)、次のハブ・アクセス・ウインドウが到着する前に、他の命令のためにさらに9サイクルを残します。

- 図1-3: コグ・ハブ相互作用 - 最善のシナリオ

図1-4は、最悪のシナリオを表します;ハブ操作はコグ0のアクセスウインドウの始まりの直後のサイクルに準備ができていました;それは、ちょうどわずかにそれを逃しました。コグは、次のハブ・アクセス・ウインドウ(15サイクル後)、そのハブ操作を実行する(7サイクル)合計22サイクルまで待ちます。また、他の操作が実行するハブ操作の後、次のハブ・アクセス・ウインドウが到着する前に、さらに9サイクルを要します。しばしば排他的な資源にアクセスしなければならないプロペラ・アッセンブリ・ルーチンから最も多くの効率を得るために、非ハブ操作に次のハブ・アクセス・ウインドウを待っているサイクルの数を少なくするようにというハブ指示をはさむことは、有益であり得ます。ほとんどのプロペラ・アッセンブリ操作は4クロック・サイクルを要することから、2つのそのような操作は隣接するハブ操作の間以外で実行できます。

- 図1-4: コグ・ハブ相互作用 - 最悪のシナリオ

特定のコグのハブ操作が、どんな形であれ、ハブ機構のおかげで、他のコグ操作のじゃまをしないことを心にとめておいてください。たとえば、コグ1が システム・クロック・サイクル2でハブ操作を始めるかもしれません。これらふたつの例において、おそらくどんな悪影響もなくコグ0は重複動作します。一方、他がしていることに関係なく、他の全てのコグは非ハブ操作を実行するか、その個々のハブ・アクセス・ウインドウを待ち続けることができます。

I/Oピン

プロペラは32本のI/Oピンを持っています。そして、そのうちの28本は正真正銘の汎用です。残る4本のI/Oピン(28 - 31)は起動時に特別な用途がありますが、起動後、汎用として使用できます;18ページの起動時手順の部を参照してください。起動後、I/Oピンが共有資源のひとつになった時から、全てのI/Oピンはどのコグからでも何時でも使用可能です。ふたつのコグが実行時に異なる目的のために同じI/Oピンを使おうとしないことの確証はアプリケーション開発者に委ねられます。

それぞれのコグは、それ自身の32ビットI/O方向レジスタと32ビットI/O出力レジスタを備えています。それぞれのコグのI/O方向レジスタの状態は、前段のコグのI/O方向レジスタとの論理和です。同様に、それぞれのコグのI/O出力レジスタの状態は、前段のコグのI/O出力レジスタとの論理和です。それぞれのコグのI/O出力レジスタの状態は、その内部のI/Oハードウエアの状態から生成され、それがすべてI/O方向レジスタの状態との論理積であることに注意が必要です。その結果、それぞれのI/Oピンの方向と出力状態は全コグ集団の「ワイヤード-OR」となります。コグの間の電気主張は可能ではありません、それでも、それらすべては同時にI/Oピンにまだアクセスすることができます!

このI/Oピン配線構成の結果は、以下の単純な規則で簡単に記述できます:

- A. 全て のコグが出力に設定されない場合だけ、ピンは入力設定です。

- B. 出力に設定された全て のコグの出力がロー・レベルの場合だけ、ピンはロー・レベルを出力します。

- C. 出力に設定されたコグの出力のどれかがハイ・レベルの場合、ピンはハイ・レベルを出力します。

表1-4は、特定の I/O ピン(この例では P12)に対する総体的なコグの影響の2、3の可能な組合せを示します。簡略化のために、これらの例では、他のコグの I/O 出力レジスタ・ハードウェアのビット 12 がゼロ(0)でクリアされると仮定します。

| 表1-4:I/O共有の例 | ||||

|---|---|---|---|---|

| Bit12ofCogs'I/O | Bit12ofCogs'I/O | State of I/O Pin | Rule | |

| Direction Register | Output Register | P12 | Followd | |

| Cog ID | 01234567 | 01234567 | ||

| Example 1 | 00000000 | 00000000 | Input | A |

| Example 2 | 10000000 | 00000000 | Output Low | B |

| Example 3 | 10000000 | 10000000 | Output High | C |

| Example 4 | 10000000 | 01000000 | Output Low | B |

| Example 5 | 11000000 | 01000000 | Output High | C |

| Example 6 | 11111111 | 01010000 | Output High | C |

| Example 7 | 11111111 | 00010000 | Output High | C |

| Example 8 | 11101111 | 00010000 | Output Low | B |

注:I/O方向レジスタはI/Oピンを、対応する場所を1に設定するとにより出力方向に、0に設定するとにより入力方向にします。

停止するコグは、他の能動コグが制御しているI/Oピンの最終的な状態に影響するので、その方向レジスタと出力状態をゼロ・クリアして、事実上影響を取り除きます。

それぞれのコグは、それ自身の32ビット入力レジスターを備えています。この入力レジスターは、本当は疑似レジスターです;入力または出力方向に関係なく、それが読み込まれるたびに、I/Oピンの現状は読み込まれます。

システム・カウンター

システム・カウンターは、システム・クロック毎に増加する、大域的なリード・オンリー・32ビット・カウンターです。コグはタイミング計算を実行するためにシステム・カウンタ(184ページの CNT レジスタ)を読み込むことができて、彼らのプロセス以内で効果的遅れを引き起こすために、WAITCNT命令(322ページ)を使うことができます。システム・カウンターは、共有資源です。あらゆるコグは、同時にそれを読み込むことができます。 システム・カウンターは、開始時からの絶対的な実時間ではなく、相対的な差分にすぎません。コグが時間内の特定の一定の瞬間からの時間の経過を追う必要があるならば、それは単純に時間内のその瞬間に最初のカウンタの値を読んで、保存して、その初期値に対して後のカウンタの値の全てを比較する必要があります。

CLK レジスタ

CLKレジスターは、システム・クロック構成の制御、すなわち供給源と種類を決定します。正確にいうと、CLKレジスターは、RC 発信器、クロック PLL、水晶発信器とクロック選択回路を構成します。(20ページの上のプロペラ・チップ。ブロック図:図1-2参照)それは_CLKMODE宣言によってコンパイル時に構成でき、CLKSET命令を通して実行時に書き込むことができます。CLK レジスタが書き込まれるときは、クロック源移行として約75μsの大域的な遅延が生じます。

このレジスターを変更するときは、書かれる値のコピーをClock Mode の位置(それは、主記憶装置 RAMのBYTE[4]です)に置かなければなりません、そして、このデータを参照してタイミング計算をするために現在の情報が明確になるように、結果として生じるマスター・クロック周波数をClock Frequency の位置(それは、主記憶装置 RAMのLONG[0]です)に書かなければなりません。(CLKMODE[179ページ]とCLKFREQ[175ページ]参照)可能ならば、妥当な情報で自動的に上記のすべての場所を更新できる CLKSET命令(183ページ)を使うことをお勧めします。

| 表1-5:CLK レジスター構造 | ||||||||

|---|---|---|---|---|---|---|---|---|

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | RESET | PLLENA | OSCENA | OSCM1 | OSCM0 | CLKSEL2 | CLKSEL1 | CLKSEL0 |

| 表1-6:RESET(Bit7) | |

|---|---|

| Bit | 効果 |

| 0 | あなたがチップをリセットするつもりでない限り、常に「0」をここに書いてください。 |

| 1 | ハードウェア・リセットと同様にチップを再起動します。Spin言語の REBOOT 命令は RESET_ビットに「1」を書き込みます。 |

| 表1-7:PLLENA(Bit6) | |

|---|---|

| Bit | 効果 |

| 0 | PLL回路を無効にします。_CLKMODE宣言のRCFASTとRCSLOWセッティングは、このようにPLLENAを構成します。 |

| 1 | PLL回路を使用可能にします。_CLKMODE宣言のPLLxxセッティングの各々は、コンパイル時にこのようにPLLENAを構成します。Clock PLLは、内部的にXINピン頻度に16を掛け算します。OSCENAは、Clock PLLにXIN信号を伝達するため「1」でなければなりません。Clock PLLの内部の頻度は、64MHz〜128MHz以内に保たれなければなりません - これは、4MHz〜8MHzのXIN周波数レンジに翻訳します。100μsを許すCLKSELxビットによってその出力のうちの1つに変わる前に安定するために、PLLを計測してください。一旦クリスタルOscillatorとClock PLL回路が使用可能にされて、安定したならば、CLKSELxビットを変えることによってすべてのクロック源の間で自由に変えることができます。 |

| 表1-8:OSCENA(Bit5) | |

|---|---|

| Bit | 効果 |

| 0 | 水晶発信器回路を無効にします。_CLKMODE宣言のRCFASTとRCSLOWセッティングは、このようにOSCENAを構成します。 |

| 1 | クロック信号がXINに入力されることができるように、あるいは、XINとXOUTが一緒にフィードバック発振器として機能することができるように、水晶発信器回路を使用可能にします。_CLKMODE宣言のXINPUTとXTALxセッティングは、このようにOSCENAを構成します。OSCMxビットは、水晶発信器回路の操作の方法を選びます。外部抵抗またはコンデンサが水晶発信子と共鳴器のために必要でないことに注意すべきです。CLKSELxビットによって水晶発信器またはClock PLL出力から水晶発信子または共鳴器にに変わる前に10ms安定させてください。水晶発信器回路を使用可能にするとき、安定化期間を共有することができるように、Clock PLLは同時に能動にされるかもしれません。 |

| 表1-9:OSCMx(Bits4:3) | ||||||

|---|---|---|---|---|---|---|

| OSCMx | CLKMODE 設定 | XOUT 抵抗値 | XIN/XOUT 容量 | 周波数範囲 | ||

| 1 | 0 | |||||

| 0 | 0 | XINPUT | 無限大 | 6pF(pad only) | DC to 128MHz Input | |

| 0 | 1 | XTAL1 | 2000Ω | 36pF | 4 to 16MHz 水晶発振子/共振器 | |

| 1 | 0 | XTAL2 | 1000Ω | 26pF | 8 to 32MHz 水晶発振子/共振器 | |

| 1 | 1 | XTAL1 | 500Ω | 16pF | 20 to 60MHz 水晶発振子/共振器 | |

| 表1-10:OSCSELx(Bits2:0) | ||||||

|---|---|---|---|---|---|---|

| CLKSELx | _CLKMODE 設定 | 主クロック | 信号源 | 備考 | ||

| 2 | 1 | 0 | ||||

| 0 | 0 | 0 | RCFAST | 〜12MHz | 内臓 | 外部ピンなし。凡そ 8MHz〜20MHz |

| 0 | 0 | 1 | RCSLOW | 〜20kHz | 内臓 | 超低消費電力。凡そ 13kHz〜33kHz |

| 0 | 1 | 0 | XINPUT | XIN | OSC | OSCENA が「1」であること。 |

| 0 | 1 | 1 | XTALx and PLL1x | XINx1 | OSC+PLL | OSCENA と PLLENA が「1」であること。 |

| 1 | 0 | 0 | XTALx and PLL2x | XINx2 | OSC+PLL | OSCENA と PLLENA が「1」であること。 |

| 1 | 0 | 1 | XTALx and PLL4x | XINx4 | OSC+PLL | OSCENA と PLLENA が「1」であること。 |

| 1 | 1 | 0 | XTALx and PLL8x | XINx8 | OSC+PLL | OSCENA と PLLENA が「1」であること。 |

| 1 | 1 | 1 | XTALx and PLL16x | XINx16 | OSC+PLL | OSCENA と PLLENA が「1」であること。 |

ロック機構

複数のコグの間でユーザー定義の資源への排他的なアクセスを容易にするために、8個のロック・ビット(別名セマフォ)が利用できます。特定の1 Long (4 Byte)以上の記憶領域がふたつ以上のコグにより使用される場合、それぞれのコグはその記憶領域の検索または読み書きを並列実行しなければなりません。これは、その記憶領域を、ひとつのコグが読み込んでいる時、もうひとつのコグが書き込みを行おうとするといった、読み書きの競合の可能性を秘めており、結果的に誤読み込み、誤書き込みが生じます。

ロック機構は、LOCKNEW, LOCKRET, LOCKSET, LOCKCLR などのハブ命令を通してハブによって操作される大域的ビットです。ロックがハブだけによって操作されるので、一時にロックに影響を及ぼせるのは唯一つのコグだけという実行支配機構を実現します。ハブはロックの使用状況の目録を維持し、コグは実行時に必要に応じてロックの生成、復帰、登録、削除が行えます。詳細な情報はLOCKNEW[230];LOCKRET[233];LOCKSET[234];LOCKCLR[228]を参照してください。

主記憶装置

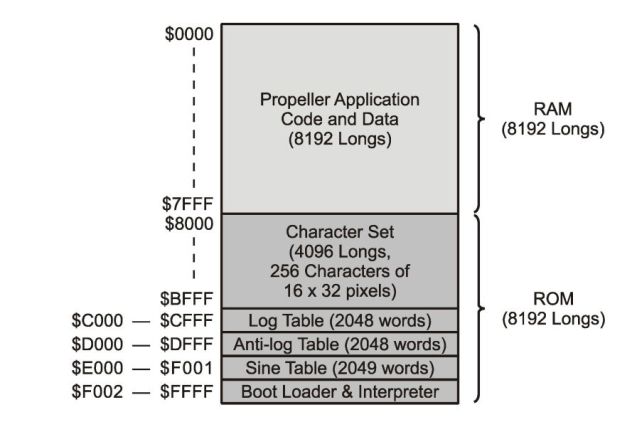

主記憶装置は、ハブによる排他的資源としてすべてのコグからアクセスできる64 kByte(16 kLong)の領域です。それは、32 kByte の RAM と 32 kByte の ROM から成ります。主記憶装置 RAMの 32 kByteは、汎用で、ホストからダウンロードされるか、外部 32 kByte の EEPROM からアップ・ロードされるプロペラ・アプリケーションの目的地です。主記憶装置 ROMの 32 kByte は、プロペラ・チップの機能に不可欠なすべてのコードとデータ資源を含みます:すなわち文字定義、対数テーブル、逆対数テーブルと三角関数テーブルとブート・ローダとSpin インタプリタです。主記憶装置組織は、図1-5に示されます。

- 図1-5:主記憶装置地図

主記憶装置 RAM

主記憶装置の前半はすべてRAMです。この場所はあなたのプログラム、データ、変数とスタック、すなわちプロペラ・アプリケーションのために使われます。チップにホストまたは外部 EEPROM からプログラムが転送されるとき、この全ての記憶場所に書き込まれます。最初の16の場所、$0000 ? $000F、はブート・ローダとインタプリタにより用いられる初期化データを格納してください。あなたのプログラムの実行コードとデータは、$0010から始まります。あなたの実行コードの後の場所は $7FFF まで、変数およびスタックの場所として使われます。

あなたのプログラムに興味深いかもしれない初期化領域に保管されるふたつの値があります:すなわち、$0000(Long)の初期マスタクロック周波数(単位ヘルツ)とそれに続く$0004(Byte)のCLK レジスターに含められる初期値です。これらの2値は物理アドレス$0000(Long)と$0004(Byte)を使って読んだり書いたりできて、かつ、あらかじめ定義された名前 CLKFREQ と CLKMODE を用いて読まれることもできます。あなたが CLOCKSET 命令を使うことなく CLK レジスターを変更するならば、参照する場合の整合性のため、これら2つの場所も更新する必要があります。

主記憶装置 ROM

主記憶装置の後半は、全ROMです。文字定義、数学機能とブート・ローダとSpin インタプリタのために使われます。

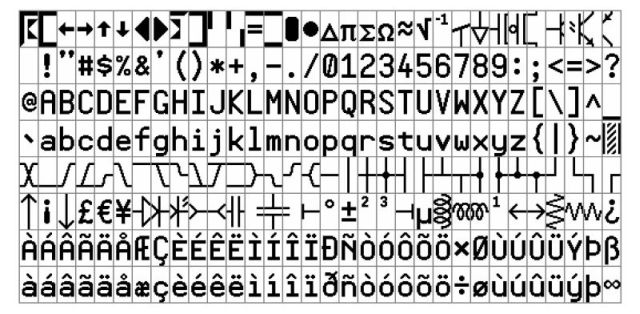

文字定義

ROMの前半は、一組の256文字定義に費やされます。各々の文字定義は、幅16ピクセル長、高さ32ピクセル長です。これらの文字定義は、ビデオディスプレイ、グラフィックLCD、印刷、その他のために使うことができます。文字セットは北アメリカ/西ヨーロッパの配置(基本的なラテン語とLatin-1拡張)に基づき、さらに多くの特殊文字が追加されています。特殊文字は、接続線と回路図の構成要素(電子工学で一般的に使われるギリシア文字)といくつかの矢と弾丸です。

- 図1-6:プロペラ・フォント文字

文字定義は、図1-6のように、左から右へ上から下へ0から255へ採番されています。ROMの中では、隣接した奇数・偶数の文字が合併された32ビット長のペアとして配置されています。最初の文字ペアは、$8000-$807F(Byte)に位置します。プロペラ。ツールは、インタラクティブ文字一覧表を含み( Help→ View Character Chart …)、各々の文字がROMにあるROM Bitmap表示で確認できます。

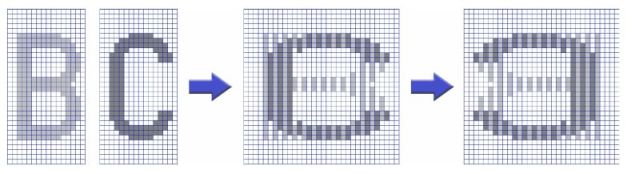

文字ペアは、16の水平ピクセルが分離され間隔を空けて隣がはさみこまれれるように列毎に併合されています。偶数文字は0,2,4、・・・30、奇数文字は1,3,5、・・・31で取得できます。図1-7で示すように、最も右のピクセルが最も高いビットであり、最も左のピクセルは最も低いビットです。これは、文字一組でピクセルの各々の列のために、1 Long(4 Byte)を構成します。この列で文字の最上列から最下列までの32列で完全な併合ペア定義を作り上げます。この定義は、コグのビデオ・ハードウエアが直接併合された列を処理することができるようにコード化され、偶数または奇数文字を表示するために色選択を行います。おまけに、立体ボタン、線分と焦点表示を描画するのに四色文字を使う実行時文字ペアを許すという長所があります(次の段落を参照してください)。

- 図1-7:プロペラ 文字 間引き

いくつかの文字コードは、避けられない意味を持ちます。例えば Tab のための 9、ラインフィードのための 10 とキャリッジリターンのための 13 などです。これらの文字コードは動作のおまじないであり、文字定義は存在しません。この理由から、それらの文字定義が、特別な4色文字のために使われました。通常の16×32ピクセルの文字単位とは対照的に、4色文字が実行時は斜縁付き三次元箱を引くために使われて、16×16ピクセルの文字単位として実装されます。それは、偶数-奇数文字ペア、0-1、8-9、10-11、12-13 を占めます。図1-8は、これらの性格のいくらかから斜縁を付加した三次元ボタンの例を示します。

- 図1-8:斜縁付き三次元ボタン

プロペラ・ツールは、ハードウエアに埋め込まれたプロペラ・フォントを模倣したParallax True Type Fontを含み、かつ使えます。このフォントとプロペラ・ツールにより、あなたのアプリケーションのため、ソースコードに、回路図、タイミング図と他の図を正に含めることができます。

対数と逆対数表

対数と逆対数表は数記法と指数記法の換算に役立ちます。数が指数記法にコード化されるとき、単純な数学活動はより複雑な影響を受けます。例えば「乗算」と「除算」は「加算」と「減算」に。「平方」は「左シフト」に「平方根」は「右シフト」に。「割る3」は「三乗根」を生じます。もう一度指数を数に逆換算すると、結果は明らかです。詳細な情報は、420 ページ「付録B:数学関数表にアクセスすること」を参照してください。

三角(sin)関数表

サイン表は、0.00439°刻みの、0°から90°までの2,049の符号なし16ビット・サイン値を提供します。90°から360°までの他の四半部のためのサイン値は、この一つの四半部サイン表で、単純な変換で計算することができます。サイン表は、角度現象に関連した計算のために使うことができます。詳細な情報は、420 ページ「付録B:数学関数表にアクセスすること」を参照してください。

ブート・ローダとSpin インタプリタ

主記憶装置 ROMの最後の領域は、プロペラ・チップのブート・ローダとSpin インタプリタ・プログラムを含みます。ブート・ローダは、パワーアップ/リセットと同時にプロペラを初期化する役割を果たします。起動時手順が始まるとき、ブート・ローダはコグ0の RAM に転送されます、そして、コグは 0 番地から始るコードを実行します。ブート・ローダ・プログラムは、コードおよびデータをダウンロードまたはアップロードするために最初にホストと EEPROM 通信ピンを検査し、 最終的に、コグ0 RAM 上で(それ自身上書きされる) Spin ・インタプリタ・プログラムを起動して使用者のプロペラ・アプリケーションを走らせる処理を行うか、または、プロペラを停止状態にします。18 ページの起動時処理の部を参照して下さい。Spin ・インタプリタ・プログラムは主記憶装置 RAM からプロペラ・アプリケーションを取ってきて実行します。アプリケーションで要求されれば、より多くの Spin コードまたはプロペラ・アセンブリ・コードを走らせるためにさらなるコグを起動するに至るかもしれません。18 ページの実行時手順を参照してください。

第二章:プロペラ・ツールを使う

大変申し訳けございませんが、この章を翻訳する気はさらさらございません。各自、オリジナルを紐解いて、当該ツールを習得されることを切望いたします。悪しからず。

非英語圏 Windows における Propeller Tool の不具合

2007年11月4日現在の Propeller Tool Ver.1.05.08 は、英米向け Windows のみの対応で、非英語圏 Windows では Parallax True Type Font が選択されません。何が書いてあるか、さっぱりわかりませんので、何とかして Parallax True Type Font を選択しなければなりません。Parallax社は、当面、暫定措置として、「コントロールパネル」「地域と言語のオプション」「詳細設定」で「英語(米国)」設定にしてもらいたいとアナウンスしていますが、この設定により動作不能となるアプリケーションが続出します。早急な対応が待たれます。

Keyword(s):[Propeller]

References: